Allion Labs | Tina Yu

Recently, the HDMI Forum has released the Compliance Test Specification (CTS) version 2.1c for Sinks. One of the highlights of HDMI 2.1 is Fixed Rate Link (FRL), which is the signaling technology used to transmit HDMI 2.1 data and enable 8K resolution.

7 Things to Know about FRL

- As its name suggests, FRL means Fixed Rate Link.

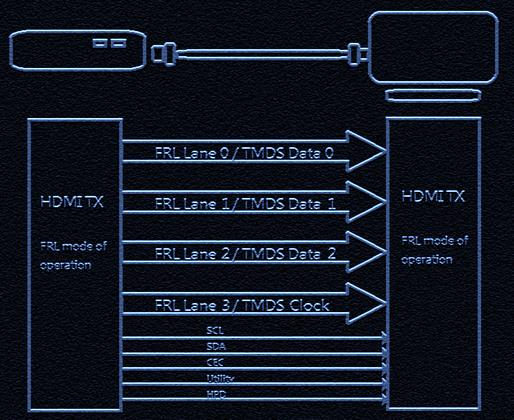

- FRL Lane 0, Lane 1, Lane 2, and Lane 3 correspond to TMDS Clock, Data 0, Data 1, and Data 2.

- Since FRL does not require a clock channel as TMDS does, FRL uses four pairs of lanes instead of three to transfer data.

- The coding of 8b/10b becomes 16b/18b, so the coding efficiency increases by 9%.

- FRL adopts VESA DSC compression technology and supports up to 10K resolution at 120Hz.

- The transmission mode of AC-coupled FRL has replaced the DC-coupled TMDS.

- FRL Link Training is compatible with TMDS.

Figure 1: Signal Structure of HDMI FRL

HDMI 2.1 FRL Enables 8K Transmission

FRL is needed to achieve 8K-quality images and higher uncompressed resolutions. FRL can simultaneously use three or four high-speed lanes for data transport. When operating in 3 Lane mode, Lane 3 shall be disabled. In 4 Lane mode, every lane can transmit data at 12Gbps. The following table shows FRL Lane link rates.

Table 1: FRL Lane Link Rates

| Number of Lanes | Rate per Lane | Total Bandwidth |

| 3 | 3 Gbps | 9 Gbps |

| 3 | 6 Gbps | 18 Gbps |

| 4 | 6 Gbps | 24 Gbps |

| 4 | 8 Gbps | 32 Gbps |

| 4 | 10 Gbps | 40 Gbps |

| 4 | 12 Gbps | 48 Gbps |

FRL Electrical Testing and Compliance

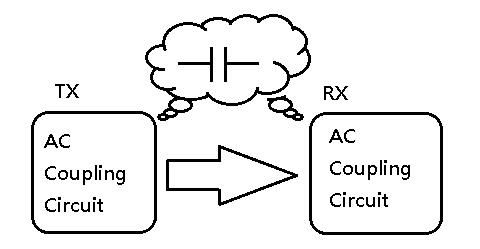

The HDMI 2.1 CTS gives a clear definition of AC Coupling Capacitor (100nF to 250nF) and AC Common Mode Noise. While TMDS only supports DC-coupling, FRL can support both DC- and AC-coupling. However, HDMI Sink has adopted DC- and AC-coupling since HDMI 1.4.

Figure 2: The AC Coupling Capacitor between TX and RX is defined as 100nF to 250nF.

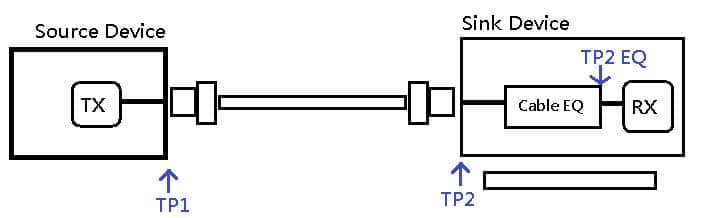

HDMI 2.1 Specification specifies TP2_EQ eye compliance test rather than TP1. The main difference is that FRL jitter characteristics include random and deterministic jitters instead of Clock Jitter.

Figure 3: Location of each test point (TP)

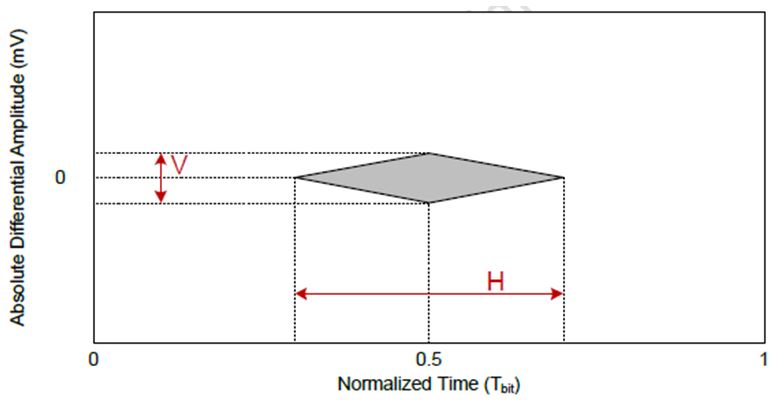

Please refer to the TP2_EQ Eye Diagram of HDMI 2.1 Specification.

Figure 4: Mask of TP2_EQ eye pattern

Table 2: Mask Specifications based on Bandwidth

| FRL Bit Rate | H | V |

| 3 Gbps | 0.5 | 150 |

| 6 Gbps | 0.4 | 150 |

| 8 Gbps | 0.385 | 135 |

| 10 Gbps | 0.37 | 120 |

| 12 Gbps | 0.35 | 100 |

FRL Protocol

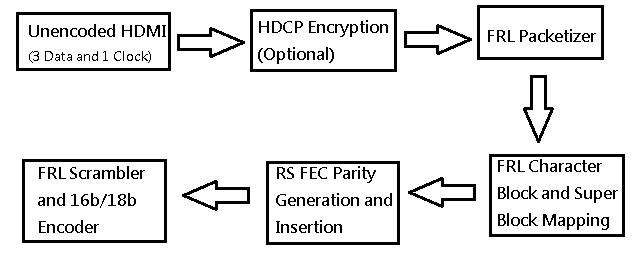

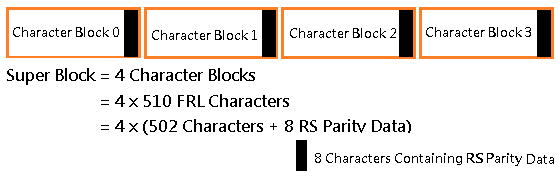

Let’s take a look at Figure 5. The first part includes three channels for data transmission and one uncompressed video channel for clock signal transmission. HDCP encryption is optional. Next, the FRL packetizer separates HDMI data into FRL packets. Each Character Block contains up to 502 FRL characters transporting FRL packets. Eight FRL characters carrying RS FEC parity data forms 510 FRL Blocks. Every four FRL Blocks construct a Super Block.

Figure 5: Specification of the FRL main protocol layer

Figure 6: The framework of Super Block

FRL Control

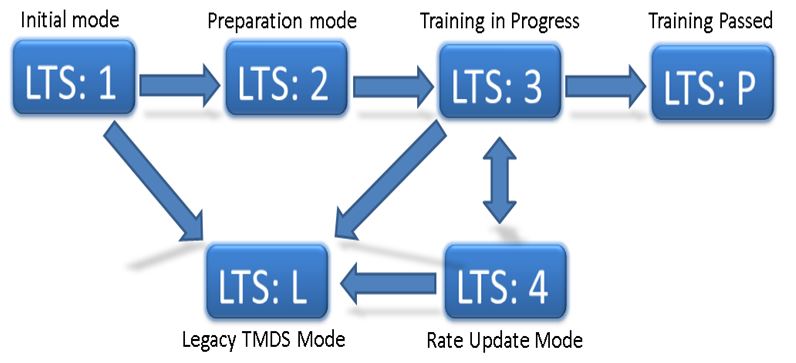

FRL Link Training is an important communication technology used to switch between TMDS and FRL. FRL Link Training is required to change FRL data rates or to start connecting for the first time. Figure 7 shows Link Training States. There are six Link Training states in total.

- LTS: 1—Source reads the Sink EDID to verify FRL support.

- LTS: 2—Source prepares for Link Training.

- LTS: 3—Source initiates Link Training. The Sink will communicate with Source at a specific FRL rate through Link Training patterns and update flag.

- LTS: 4—Sink requests new Link Rate. LTS4 is used to change FRL rates.

- LTS: P indicates that Link Training is complete and that the FRL transmission begins.

- LTS: L means that TMDS will be initiated if FRL Link Training fails.

Figure 7: A representation of Link Training States

Does FRL replace TMDS?

Although there’s not much difference between the interface and pin configurations of HDMI 2.1 and HDMI 2.0, HDMI 2.1 8K and HDMI 2.0 4K are two different types of technologies. HDMI 2.1 Specification is more stringent and complex. To support devices that use TMDS, HDMI 2.1 Specification is backward compatible with earlier versions (HDMI 1.4/2.0). This specification makes sure that products that meet HDMI 2.1 Specifications will not have compatibility issues with HDMI 1.4/2.0 products in the market.

Allion Test Solutions

Allion has prepared a comprehensive series of test solutions for 8K TV manufacturers to acquire the HDMI 2.1 compliance certification faster.

HDMI 2.1 Compliance Test

1. TMDS

- TMDS Electrical Test

- TMDS Protocol Test

- Pixel Decoding Test

- Video Timing Test

- EDID Test

- E-DDC Test

2. FRL

- FRL Electrical Test

- FRL Protocol Test

- FRL Pixel Decoding Test

- FRL Video Timing Test

- FRL E-EDID Test

HDMI 1.4 Compliance Test

- EDID/E-DDC Test

- Electrical Test

- Protocol Test

- Video Test

- Audio Test

- Interoperability with DVI Test

- Advanced Features